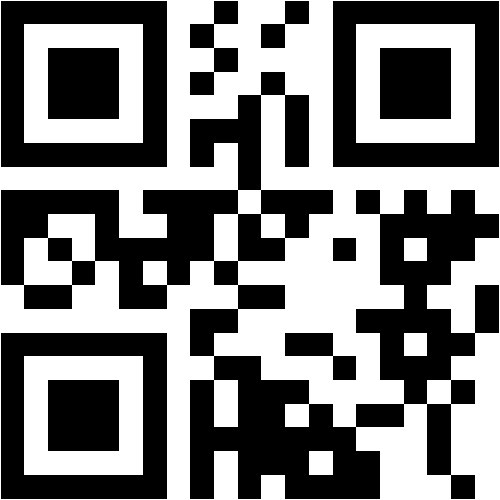

Denis

@spbstu.ru

Peter the Great St.Petersburg Polytechnic University (SPbPU)

RESEARCH INTERESTS

Microelectronics,

Scopus Publications

Scopus Publications

Ivan A. Rumyancev, Margarita O. Aivazova, and Denis B. Akhmetov

IEEE

Ivan A. Rumyancev, Denis B. Akhmetov, and Nikita V. Ivanov

IEEE

This paper presents the simulation results of a vector modulator that can be used in TX/RX front-end modules of the fifth generation communication systems. The vector modulator is designed in 130-nm SiGe technology and demonstrates RMS amplitude error below 0.2 dB and RMS phase error less than 1.2 degree in 24–30 GHz frequency band while provides about 5 dBm input 1-dB compression point with 0 dB maximum gain and 30 mW power consumption. The layout area of the designed fully integrated circuit is less than 0.5 sq. mm.

Ivan A. Rumyancev, Margarita O. Aivazova, and Denis B. Akhmetov

IEEE

Virtual reality technology improves students’ experience with laboratory equipment in the case of blended and distance education. Vector networks analyzers are widely used to measure parameters of radio frequency integrated circuits and modules. Vector network analyzers must be calibrated before measurements to eliminate systematic errors. This work-in-progress paper presents a virtual reality trainer for one or two port measurement calibration of a vector network analyzer. The developed application was tested with Oculus Quest 2 headset.

Denis B. Akhmetov, Alexander S. Korotkov, and Ivan A. Rumyancev

IEEE

Paper presents simulation and measurement results of 2.4-2.5 GHz fractional-N frequency synthesizer with integrated voltage controlled oscillator, designed in a standard 0.18 um CMOS technology process, for RFID systems. Phase noise of the designed synthesizer is below −117 dBc/Hz at 1 MHz offset. The output power is −2 dBm, while spur level is below − 79 dBc. Chip area, occupied by the designed circuit, is 1.2 sq. mm.

Denis B. Akhmetov and Alexander S. Korotkov

IEEE

Different topologies of charge pumps proposed for reference spur reduction at the output of the phased-locked loops. Usually they are based on differential topology or employ additional circuits such as operational amplifiers. The proposed solution is based on charge injection compensation technique. The modelling shows spur reduction up to 10 dB comparing to traditional approaches. Finally, the 2.4 GHz transmitter was fabricated in a 180nm UMC CMOS process. It achieves in worst case −74.4dBc at the both ends of frequency band and −79.1dBc in the center.

D. B. Akhmetov, A. S. Korotkov, D. V. Morozov, M. M. Pilipko, and I. A. Rumyancev

IEEE

RFID-tags are conventionally provided for various things. A RFID system for Internet of Nano Things based on a UMC 180nm CMOS integrated circuit was proposed. The system is intended for identification of tags realized on a surface-acoustic-wave delay lines and designed as a transceiver front-end with operating frequency range of 2.40–2.48 GHz. A polling signal is a stepped frequency chirp, and the read range makes up 3 m.

D. Akhmetov and A. Korotkov

Allerton Press