Narayan A.Badiger

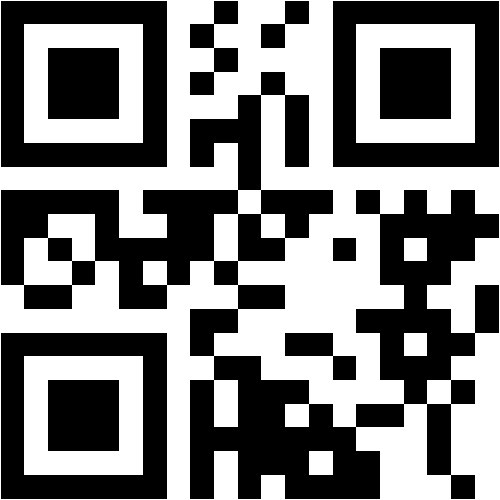

@sgbit.edu.in

Assistant Professor and E&C Dept.

S G Balekundri Institute of Technology

EDUCATION

M.Tech (PhD)

RESEARCH, TEACHING, or OTHER INTERESTS

Electrical and Electronic Engineering

Scopus Publications

Scholar Citations

Scholar h-index

Scopus Publications

Narayan A. Badiger and Sridhar Iyer

Springer Science and Business Media LLC

Narayan A. Badiger and Sridhar Iyer

IEEE

A key component in Phase-Locked Loop (PLL) circuits is Phase-Frequency Detectors (PFD), which find applications in numerous high-speed applications like processors and communication systems. The objective of this article is to design a PFD to (i) overcome the issue of high power dissipation and (ii) reduce the area of the existing design. A Cadence Virtuoso environment is used to design a proposed PFD and is implemented using Generic Process Development Kit (GPDK) 45 nm technology with a supply voltage of 1V. The outcomes represent that the proposed PFD consumes a power of 66.25 nw, which is considerably lower than the existing designs. And also, the proposed PFD is designed using 10 transistors which reduce the area in comparison to the convention of using 16 transistors or more.

Narayan A. Badiger, Sridhar Iyer, and Sujay Gejji

IEEE

The major challenge in designing and synthesizing VLSI circuits is to minimize propagation delay and Power Dissipation (Pd). This depends on the design parameters such as W/L ratio, scaling technology, and load capacitance. This paper focuses on detailed study of the propagation delay and dynamic power of a Complementary Metal Oxide Semiconductor (CMOS) inverter considering a channel length below 45nm following which, the best geometry for the minimum delay is found. For simulations, the standards of model parameters are used from the Berkeley Predictive Technology Model (PTM), and the study is performed for the technology including 16nm, 22nm, 32nm, 45nm with the help of the Electric software and LT Spice simulation tool. Our study shows that the CMOS inverter designed using the proposed methodology enhances the static and total power dissipation in comparison to the conventional design. The results demonstrate that a variation of the load capacitance leads to a change in the delay and dynamic power, and the technology scaling results in an increase of delay; however, with a decrease in the dynamic power values.